Error Correcting Code (ECC) RAM improves data reliability in workstations and servers by detecting and correcting single-bit errors, preventing data corruption.

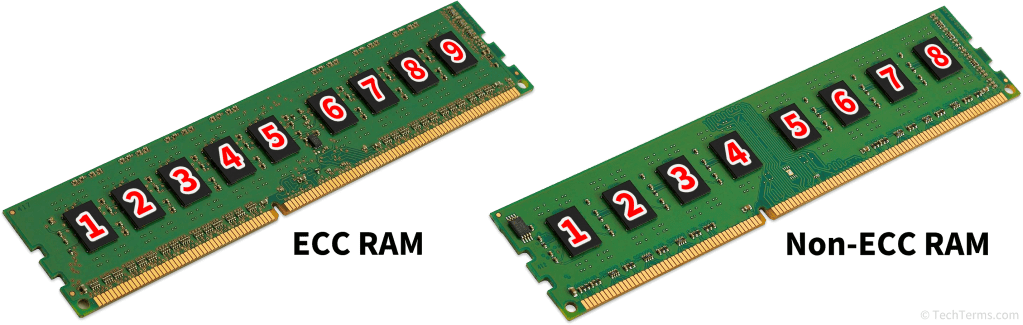

ECC memory adds 8 extra bits for every 64-bit word, resulting in a 72-bit data bus, enabling error detection and correction mechanisms.

Registered DIMMs (RDIMMs) incorporate a register between the memory module and memory controller, reducing electrical load and improving stability in high-capacity systems.

UDIMMs (Unbuffered DIMMs) lack this register, offering lower latency but less stability at large memory scales.

ECC memory can correct single-bit errors and detect (but not correct) multi-bit errors (2-bit, 3-bit, or 4-bit errors), where the system generates an error message and halts operation.

ECC operates using Hamming code or cyclic redundancy check (CRC) algorithms, depending on implementation.

Most server-grade motherboards support either UDIMMs or RDIMMs, but not both, and ECC functionality requires both the motherboard and CPU to support it.

Mixing ECC and non-ECC memory modules, or RDIMMs and UDIMMs, typically results in a system failure to boot.

BitcoinVersus.Tech Editor’s Note:

We volunteer daily to ensure the credibility of the information on this platform is Verifiably True. If you would like to support to help further secure the integrity of our research initiatives, please donate here

BitcoinVersus.tech is not a financial advisor. This media platform reports on financial subjects purely for informational purposes.

Leave a comment